OB-XA-R1

This is a set of two replacement program ROMs for the Oberheim OB-Xa synthesizer, preprogrammed with the latest OB-Xa software revision (XA-GA0 and XA-G1) released in February 1982.

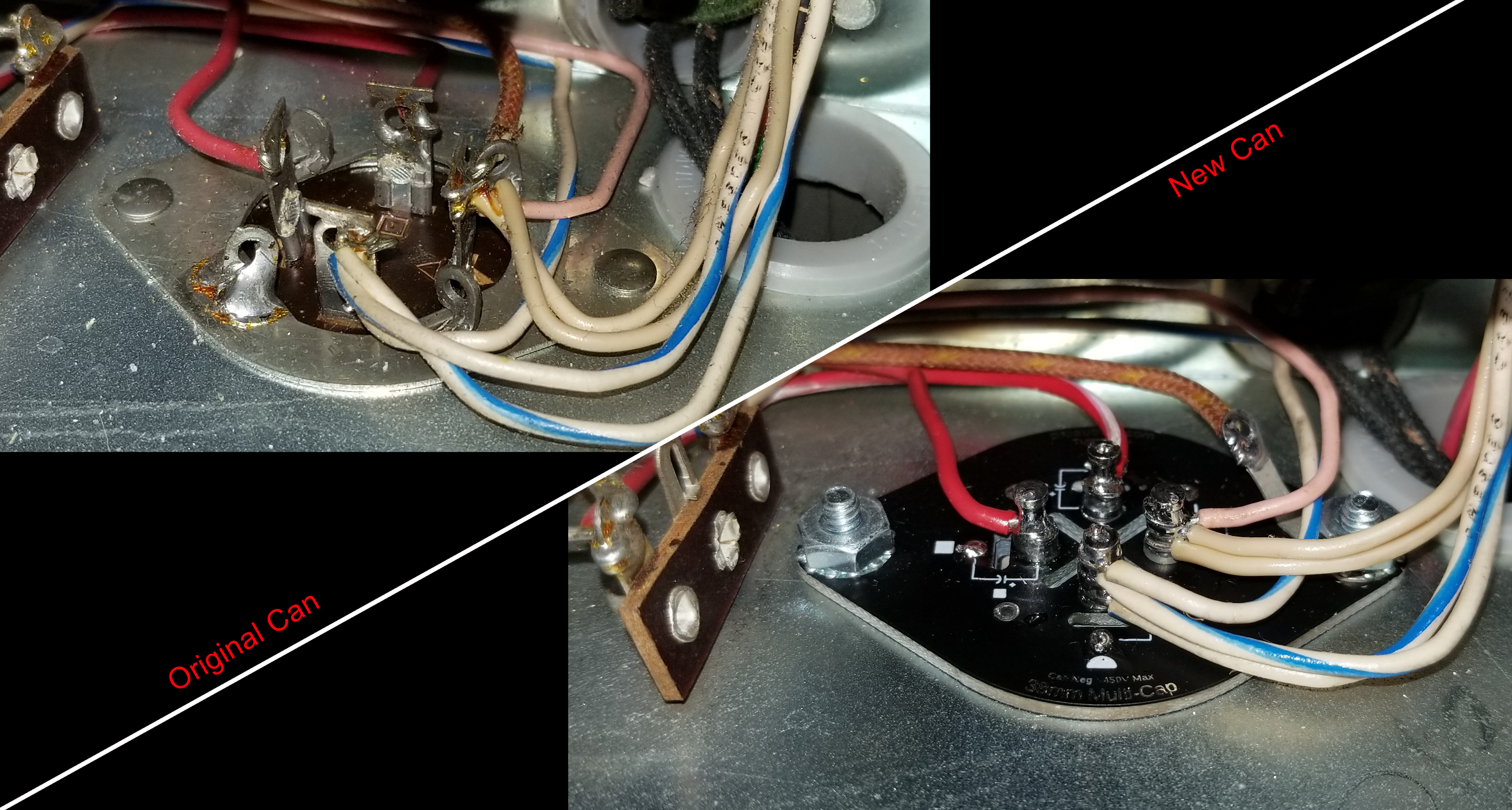

The new ROMs are based around modern CMOS EEPROM devices manufactured by Atmel Corporation (now a part of Microchip), adapted to a 24-pin DIP footprint with a custom PCB and gold plated pins. These devices are fully compatible with the original NMOS UV EPROMS (ST M2732A-2), have TTL and CMOS compatible inputs and outputs, and offer a significant reduction in current draw: up to a 68% decrease under normal operating conditions, and up to a 94% decrease in standby mode.

All ROM boards are hand assembled in the USA and tested in an Oberheim OB-Xa to guarantee their functionality.

If you are ordering these to repair an OB-Xa with a nonfunctional computer, please note that in our experience it is not uncommon for these units to have one or more dead logic ICs on the upper or lower control boards. Thus, it is possible that your original ROMs are fine, but another component in the system has failed.

ROM CRC-32 Checksums:

XA-GA0: F8268EA0

XA-G1: B32DCB5D